### CP302

### 3U CompactPCI Pentium III-based CPU Board

Manual ID 21112, Rev. Index 05 Feb 01

The product described in this manual is in compliance with all applied CE standards.

This page was intentionally left blank.

Preface

## **Table of Contents**

### Preface

| Manual Table of Contents                    | 0 - 3  |

|---------------------------------------------|--------|

| Revision History                            | 0 - 14 |

| Trademarks                                  | 0 - 14 |

| Explanation of Symbols                      | 0 - 15 |

| For Your Safety                             | 0 - 16 |

| High Voltage Safety Instructions            | 0 - 16 |

| Special Handling and Unpacking Instructions | 0 - 16 |

| General Instructions on Usage               | 0 - 17 |

| Two Year Warranty                           | 0 - 18 |

### Introduction

| 1.1 | Intr | roduction to CompactPCI1 - 3               |

|-----|------|--------------------------------------------|

| 1.2 | PE   | P Single-height CPU Boards1 - 4            |

| 1.3 | CP   | 302 Product Overview1 - 4                  |

| 1.4 | CP   | 302 Board Introduction1 - 5                |

| 1.5 | CP   | 302 Main Specifications1 - 6               |

| 1.6 | Ροι  | wer Consumption and Temperature Range1 - 8 |

| 1.  | 6.1  | Temperature Range1 - 10                    |

|     | 1.6  | 1.1.1 Temperature Range and Air Flow1 - 10 |

| 1.7 | Sof  | ftware Support1 - 11                       |

| 1.8 | Ар   | olied Standards1 - 12                      |

| 1.  | 8.1  | CE Compliance                              |

| 1.  | 8.2  | Mechanical Compliance1 - 12                |

| 1.  | 8.3  | Environmental Tests1 - 12                  |

| 1.9 | Rel  | lated Publications1 - 12                   |

| 1.  | 9.1  | CompactPCI Systems/Boards1 - 12            |

### Preface

Chapter 2

| 2.1 | Fur  | ctional Block Diagram2 - 4                    |

|-----|------|-----------------------------------------------|

| 2.2 |      | nt Panels                                     |

| 2.3 |      | ard Layouts                                   |

| 2.4 |      | <i>in Features</i>                            |

| 2   | .4.1 | CPU                                           |

| 2   | .4.2 | Memory                                        |

| 2   | .4.3 | Interrupts                                    |

| 2.5 | Per  | ipherals                                      |

| 2   | .5.1 | Watchdog Timer                                |

| 2   | .5.2 | Battery                                       |

| 2   | .5.3 | Reset                                         |

| 2   | .5.4 | SMBus Devices                                 |

| 2   | .5.5 | Thermal Management / System Monitoring 2 - 11 |

| 2   | .5.6 | Serial EEPROM                                 |

| 2   | .5.7 | Flash Memory                                  |

| 2   | .5.8 | PCI- to-PCI Bridge                            |

| 2.6 | Boa  | ard Interfaces                                |

| 2   | .6.1 | Keyboard/Mouse Connector                      |

|     | 2.6. | 1.1 Keyboard Connector CON4 Pinout            |

| 2   | .6.2 | USB Connector CON5                            |

|     | 2.6. | 2.1 USB Connector CON5 Pinout                 |

| 2   | .6.3 | VGA Interface                                 |

|     | 2.6. | 3.1 VGA connector CON8 Pinout                 |

| 2   | .6.4 | Fast Ethernet                                 |

|     | 2.6. | 4.1 RJ45 Connector CON10 Pinout               |

| 2   | .6.5 | Ethernet LED Status                           |

| 2   | .6.6 | Fan Power Supply                              |

| 2   | .6.7 | EIDE Interfaces                               |

|     | 2.6. | 7.1 EIDE Connector CON7 Pinout                |

| 2.6.8 Floppy Drive Interface2 - 21                     |

|--------------------------------------------------------|

| 2.6.8.1 Floppy Disk Connector CON13 Pinout             |

| 2.6.8.2 PCI Extension Connector CON62 - 22             |

| 2.6.8.3 I/O Interface Connectors CON3 and CON11        |

| 2.6.9 CompactPCI Bus Interface(s)2 - 22                |

| 2.6.9.1 CompactPCI Connectors CON1 and CON2 Pinouts    |

| 2.6.10 Rear I/O Interface2 - 25                        |

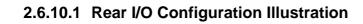

| 2.6.10.1 Rear I/O Configuration Illustration           |

| 2.6.10.2 Optional Rear I/O on CPCI Connector CON2      |

| 2.6.10.3 Rear I/O Jumper Setting2 - 28                 |

| 2.7 Jumper Description2 - 30                           |

| 2.7.1 External BIOS2 - 30                              |

| 2.7.2 Memory Type Selection2 - 30                      |

| 2.7.3 Flash Type Selection2 - 30                       |

| 2.7.4 Fan Power Supply Selection2 - 31                 |

| 2.7.5 PCI VI/O setting2 - 31                           |

| 2.7.6 Shorting Chassis GND (Shield) to Logic GND2 - 31 |

| 2.7.7 Jumper Setting for Rear I/O2 - 32                |

| 2.7.8 Reserved Jumpers2 - 33                           |

| 2.8 Memory Map                                         |

| 2.9 Special Registers Description                      |

| 2.9.1 Watchdog2 - 35                                   |

| 2.9.1.1 Watchdog Trigger2 - 35                         |

| 2.9.1.2 Watchdog Timer2 - 36                           |

| 2.9.2 Reset Control Register2 - 36                     |

| 2.9.3 Interrupt Configuration Register2 - 37           |

| 2.9.4 I/O Status2 - 38                                 |

| 2.9.5 Board ID2 - 38                                   |

| 2.9.6 Hardware Index2 - 39                             |

| 2.9.7 Jumper Status2 - 39                              |

| 2.9.8 Logic Version2 - 40                              |

| 2.9.9 PCI Interrupt Routing2 - 40                      |

| 2.9.10 Memory Management of Flash Socket               |

| 2.9.11 Flash Socket Page2 - 41                         |

| 2.10 Video Resolutions2 - 42                           |

### Installation

| 3.1 | Boa | ard Installation         | 3 - 3 |

|-----|-----|--------------------------|-------|

| З.  | 1.1 | Placement of the CP302   | 3 - 4 |

| З.  | 1.2 | EIDE Interfaces          | 3 - 4 |

| 3.  | 1.3 | Keyboard/Mouse Connector | 3 - 5 |

| 3.2 | Sof | tware Installation       | 3 - 5 |

### **CMOS Setup**

| 4.1  | Proprietary Notice     | 4 - 3  |

|------|------------------------|--------|

| 4.2  | Introduction to Setup  | 4 - 3  |

| 4.3  | Main Setup Menu        | 4 - 7  |

| 4.4  | Standard CMOS Setup    | 4 - 9  |

| 4.5  | BIOS Features Setup    | 4 - 13 |

| 4.6  | Chipset Features Setup | 4 - 18 |

| 4.7  | Power Management       |        |

| 4.8  | PM Timers              | 4 - 23 |

| 4.9  | PNP/PCI Configuration  | 4 - 24 |

| 4.10 | Integrated Peripherals | 4 - 26 |

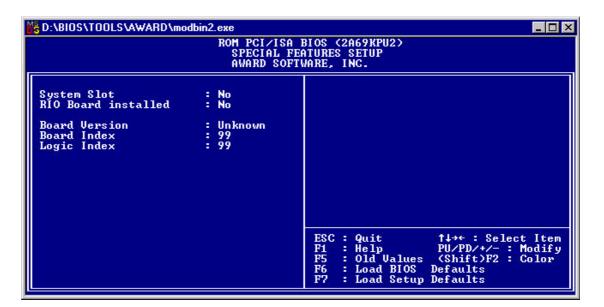

| 4.11 | Special Setup Features | 4 - 29 |

| 4.12 | Password Setting       | 4 - 30 |

| 4.13 | POST Messages          | 4 - 31 |

| 4.14 | POST Codes             | 4 - 35 |

### I/O Module

| A.1 | Overview                                             | A - 3  |

|-----|------------------------------------------------------|--------|

| A.2 | Technical Specifications                             | A - 3  |

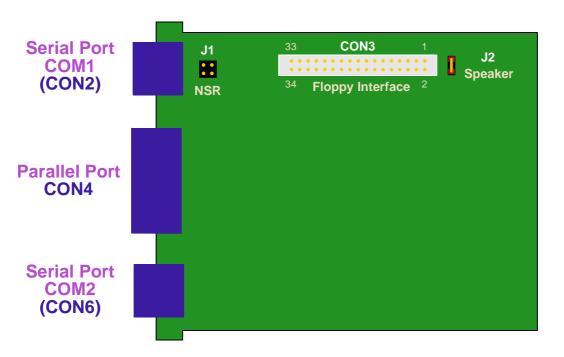

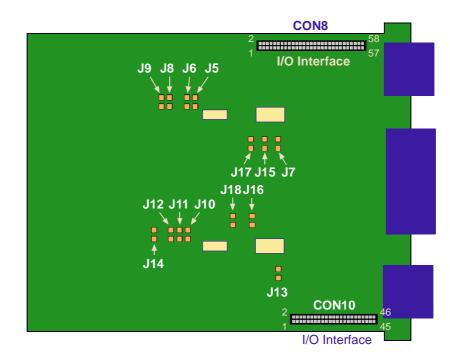

| A.3 | Module Layouts                                       | A - 4  |

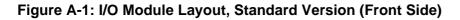

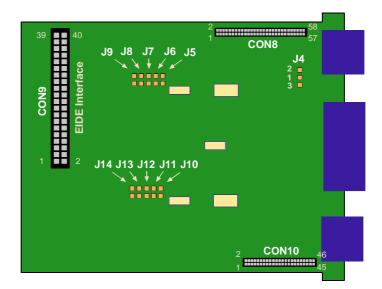

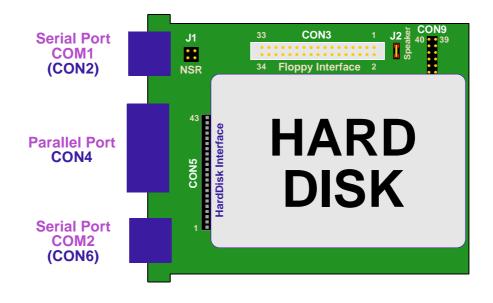

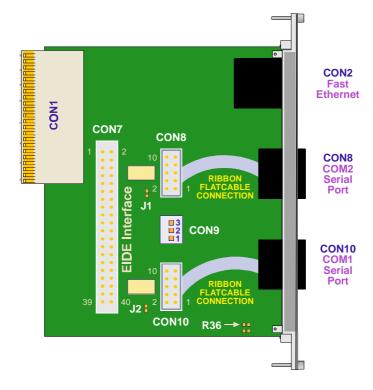

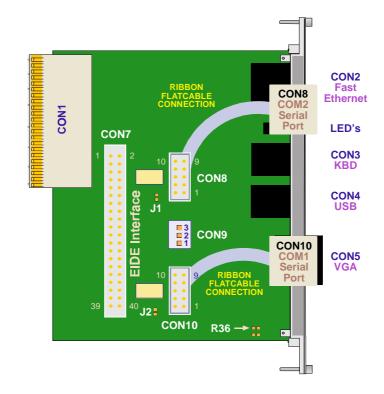

| A.  | .3.1 Standard I/O Module Layout                      | A - 4  |

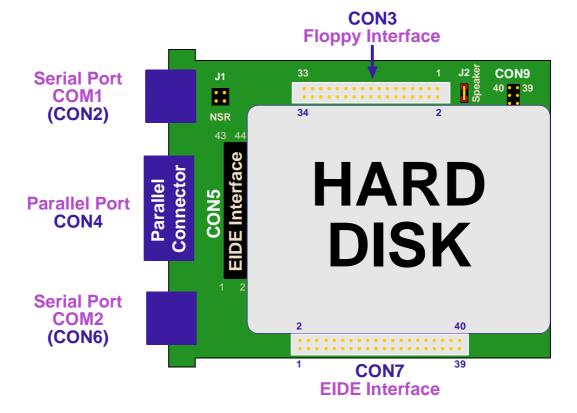

| A.  | .3.2 HardDisk I/O Module Layout                      | A - 5  |

| A.4 | Module Interfaces (Front Panel and Onboard)          | A - 6  |

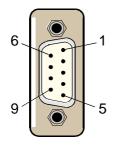

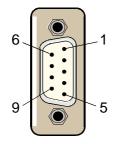

| A.  | .4.1 Serial Port Interfaces                          | A - 6  |

|     | A.4.1.1 Serial Port Connectors CON2 and CON6 Pinouts | A - 6  |

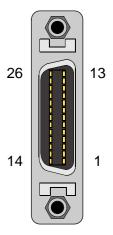

| A.  | .4.2 Parallel Port Interface                         | A - 7  |

|     | A.4.2.1 Parallel Port Connector CON4 Pinout          | A - 8  |

| А.  | .4.3 Onboard IDE Connector CON5 Pinout               | A - 9  |

| А.  | .4.4 EIDE Connector CON9 Pinout                      | A - 11 |

| А.  | .4.5 Floppy Drive Interface                          | A - 13 |

|     | A.4.5.1 Floppy Drive Connector CON3 Pinout           | A - 13 |

| A.  | .4.6 I/O Interface Connectors (CON8 and CON10)       | A - 14 |

| A.5 | Jumper Description                                   | A - 14 |

| A.  | .5.1 Serial Port Setting                             | A - 14 |

# Appendix **B**

### PMC and CompactPCI Expansion Module

| B.1 | Overview                                | B - 3 |

|-----|-----------------------------------------|-------|

| B.2 | Technical Specifications                | В-З   |

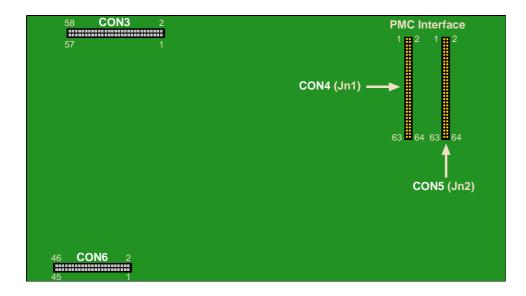

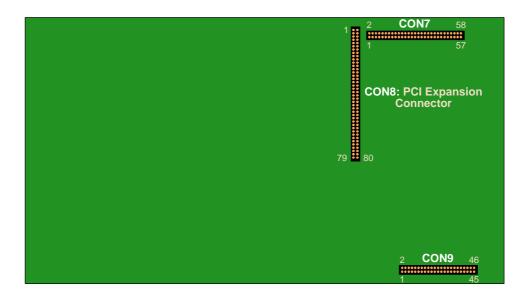

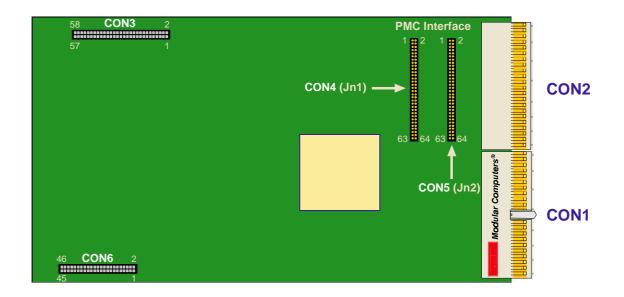

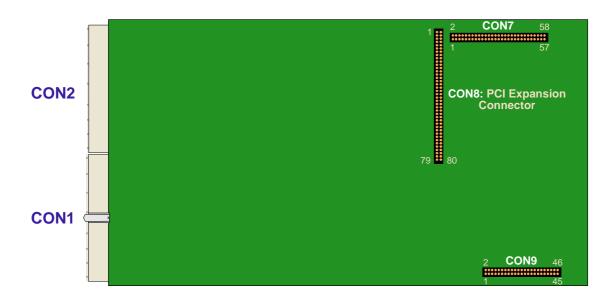

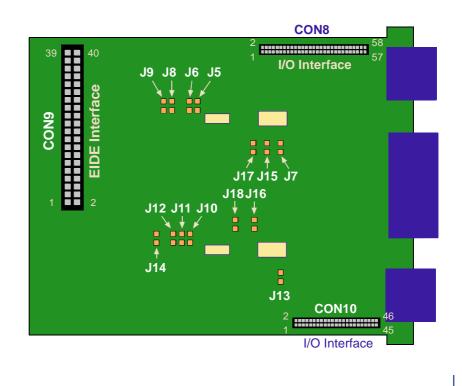

| B.3 | Module Layout                           | B - 4 |

| B.4 | Module Interfaces                       | B - 6 |

| B.  | 4.1 PCI Extension Connector CON8        | B - 6 |

| B.  | 4.2 PMC Interface                       | B - 6 |

|     | B.4.2.1 PMC Interface Jn1 (CON4) Pinout | B - 7 |

|     | B.4.2.2 PMC Interface Jn2 (CON5) Pinout | B - 8 |

|     |                                         |       |

| В   | .4.3 | CompactPCI Bus Interface                             | 3 - 9 |

|-----|------|------------------------------------------------------|-------|

|     | B.4. | .3.1 CompactPCI Bus Connectors CON1 and CON2 Pinouts | 3 - 9 |

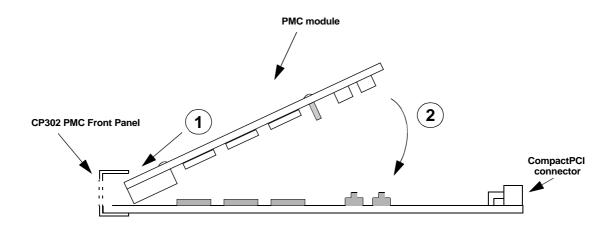

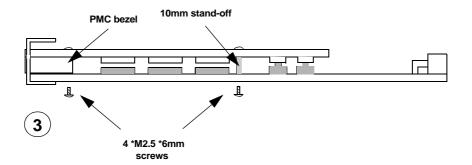

| B.5 | Boa  | ard InstallationB                                    | - 11  |

### **IDE2** Module

| C.1 Overview                                         | C-3    |

|------------------------------------------------------|--------|

| C.2 Technical Specifications                         | C-3    |

| C.3 Module Layouts                                   | C-4    |

| C.3.1 Standard IDE2 Module Layout                    | C - 4  |

| C.3.2 HardDisk IDE2 Module Layout                    | C - 5  |

| C.4 Module Interfaces (Front Panel and On-board)     | C-6    |

| C.4.1 Serial Port Interfaces                         | C - 6  |

| C.4.1.1 Serial Port Connectors CON2 and CON6 Pinouts | C - 7  |

| C.4.2 Parallel Port Interface                        | C-8    |

| C.4.2.1 Parallel Port Connector CON4 Pinout          | C-8    |

| C.4.3 EIDE Interface                                 | C - 9  |

| C.4.3.1 Onboard EIDE Connector CON5 Pinout           | C - 9  |

| C.4.3.2 EIDE Connectors CON7 and CON9 Pinouts        | C - 11 |

| C.4.4 Floppy Drive Interface                         | C - 13 |

| C.4.4.1 Floppy Drive Connector CON3 Pinout           | C - 13 |

| C.4.5 I/O Interface Connectors (CON8 and CON10)      | C - 14 |

| C.4.6 Speaker Connector J2                           | C - 14 |

| C.5 Jumper Description                               | C - 14 |

| C.5.1 Serial Port Setting                            | C - 14 |

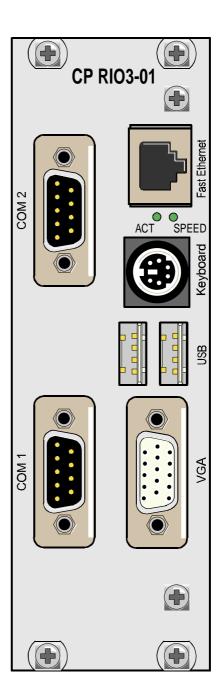

### CP-RIO3-01 Rear I/O Module

| D.1 | Overview                                              | D - 3  |

|-----|-------------------------------------------------------|--------|

| D.2 | Front Panels                                          | D - 4  |

| D.3 | Module Layout: 4HP and 8HP Versions                   | D - 5  |

| D.4 | Module Interfaces                                     | D - 6  |

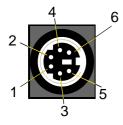

| D   | .4.1 Keyboard/Mouse Interface                         | D - 6  |

|     | D.4.1.1 Keyboard Connector CON3 Pinout                | D - 6  |

| D   | .4.2 USB Interfaces                                   | D - 7  |

|     | D.4.2.1 USB Connector CON4 Pinout                     | D - 7  |

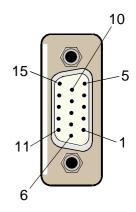

| D   | .4.3 VGA Interface                                    | D - 8  |

|     | D.4.3.1 VGA Connector CON5 Pinout                     | D - 8  |

| D   | .4.4 Fast Ethernet Interface                          | D - 9  |

|     | D.4.4.1 RJ45 Connector CON2 Pinout                    | D - 9  |

| D   | 4.5 Ethernet LED Status                               | D - 9  |

| D   | .4.6 Serial Port Interfaces                           | D - 10 |

|     | D.4.6.1 Serial Port Connectors CON8 and CON10 Pinouts | D - 10 |

| D   | .4.7 Fan Control Interface (Optional)                 | D - 11 |

|     | D.4.7.1 Fan Control Connector CON9 Pinout             | D - 11 |

| D   | 4.8 EIDE Interface                                    | D - 11 |

|     | D.4.8.1 EIDE Connector IDE2 (CON7) Pinout             | D - 11 |

| D   | .4.9 Rear I/O interface on CompactPCI Connector CON1  | D - 13 |

|     | D.4.9.1 CompactPCI Connector CON1 Pinout              | D - 13 |

| D.5 | Jumper Setting                                        | D - 14 |

| D   | 5.1 COM Port Configuration                            | D - 14 |

|     | D.5.1.1 COM1 Configuration                            | D - 14 |

|     | D.5.1.2 COM2 Configuration                            | D - 14 |

| D   | .5.2 Shorting Chassis GND (Shield) to Logic GND       | D - 15 |

### Preface

## Figures

### Figure Number and Title

| 2-1         | CP302 Functional Block Diagram2 - 4                                  |

|-------------|----------------------------------------------------------------------|

| 2-2         | CP302 Front Panels                                                   |

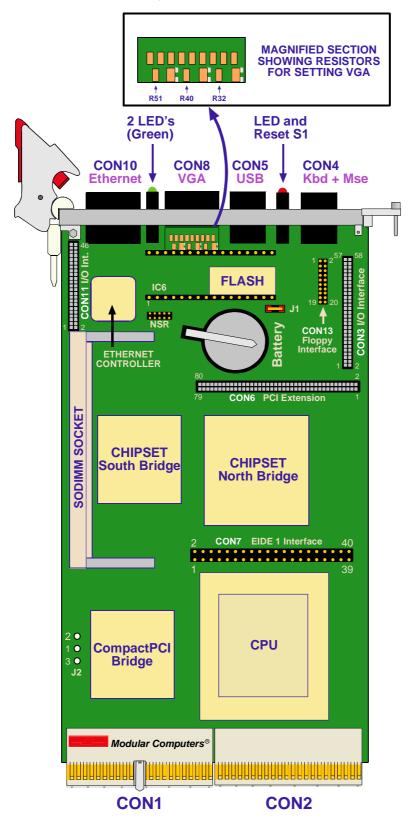

| 2-3         | CP302 Board Layout (Front Side)2 - 6                                 |

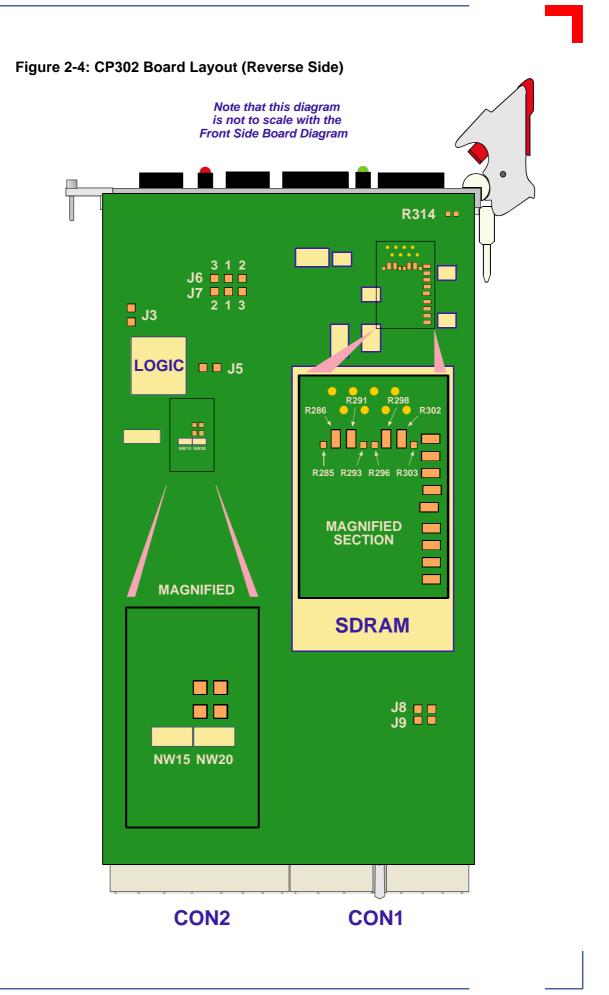

| 2-4         | CP302 Board Layout (Reverse Side)2 - 7                               |

| 2-5         | Keyboard/Mouse Connector2 - 14                                       |

| 2-6         | USB Connector                                                        |

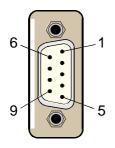

| 2-7         | DSUB VGA Connector                                                   |

| 2-8         | Ethernet/Fast Ethernet Connector                                     |

| 2-9         | CP302 Rear I/O Configuration2 - 26                                   |

| 4-1         | CMOS Setup Utility Main Menu — Screen Display                        |

| 4-2         | Standard CMOS Setup Menu — Screen Display 4 - 9                      |

| 4-3         | BIOS Features Setup — Screen Display 4 - 13                          |

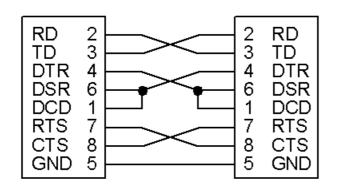

| 4-4         | Null-Modem Cable Connection 4 - 17                                   |

| 4-5         | Chipset Features Setup — Screen Display                              |

| 4-6         | Power Management Setup — Screen Display                              |

| 4-7         | PNP/PCI Configuration — Screen Display 4 - 26                        |

| <b>4-</b> 8 | Integrated Peripherals — Screen Display 4 - 28                       |

| 4-9         | Special Features Setup — Screen Display 4 - 31                       |

| A-1         | I/O Module Layout, Standard Version (Front Side)A - 4                |

| A-2         | I/O Module Layout, Standard Version (Reverse Side)A - 4              |

| A-3         | I/O Module Layout, Hard Disk Version (Front Side)A - 5               |

| A-4         | PC-compatible D-Sub Serial InterfaceA - 6                            |

| A-5         | PC-compatible D-Sub Parallel InterfaceA - 7                          |

| B-1         | PMC Module Layout, Version without CPCI Connectors (Front View)B - 4 |

| B-2         | PMC Module Layout, Version without CPCI Connectors (Rear View)B - 4  |

| B-3         | PMC Module Layout, Version with CPCI Connectors (Front View)B - 5    |

| B-4         | PMC Module Layout, Version with CPCI Connectors (Rear View)B-5       |

| B-5         | Installation DiagramsB - 12                                          |

| C-1         | IDE2 Module Layout, Standard Version (Front Side)C - 4               |

| C-2 | IDE2 Module Layout, Standard Version (Reverse Side) | C - 4  |

|-----|-----------------------------------------------------|--------|

| C-3 | IDE2 Module Layout, HardDisk Version (Front Side)   | C - 5  |

| C-4 | IDE2 Module Layout, HardDisk Version (Reverse Side) | C - 5  |

| C-5 | PC-Compatible D-sub Serial Interface                | C - 6  |

| C-6 | PC-Compatible Parallel Interface                    | C - 8  |

| D-1 | CP-RIO3-01 Front Panels, 4HP and 8HP Versions       | D - 4  |

| D-2 | CP-RIO3-01 Module Layout, 4HP Version               | D - 5  |

| D-3 | CP-RIO3-01 Module Layout, 8HP Version               | D - 5  |

| D-4 | Keyboard/Mouse Connector                            | D - 6  |

| D-5 | USB Connector CON4                                  | D - 7  |

| D-6 | D-sub VGA Connector                                 | D - 8  |

| D-7 | Ethernet/Fast Ethernet Connector                    | D - 9  |

| D-8 | PC-Compatible D-sub Serial Interface                | D - 10 |

## Tables

### Table Number and Title

| 1-1  | CP302 Main Specifications1 - 6                      |

|------|-----------------------------------------------------|

| 1-2  | Power Consumption Table with DOS Running1 - 8       |

| 1-3  | Power Consumption Table with Windows NT 4.0 Running |

| 1-4  | Power Consumption Table for CP302 Accessories       |

| 1-5  | Typical Temperature Range and Required Air Flow     |

| 2-1  | Memory Options Utilizing SODIMM Sockets             |

| 2-2  | SMBus Device Addresses                              |

| 2-3  | EEPROM Address Map2 - 12                            |

| 2-4  | Keyboard Connector CON4 Pinout2 - 14                |

| 2-5  | USB Connector CON5 Pinout2 - 15                     |

| 2-6  | VGA connector CON8 Pinout2 - 16                     |

| 2-7  | RJ45 Connector CON10 Pinout2 - 17                   |

| 2-8  | Fan Power Supply2 - 18                              |

| 2-9  | AT Standard Connector CON7 Pinout2 - 19             |

| 2-10 | Floppy Disk Connector CON13 Pinout2 - 21            |

| 2-11 | CompactPCI Bus Connector J1 (CON1) Pinout 2 - 23        |

|------|---------------------------------------------------------|

| 2-12 | 64-bit CompactPCI Bus Connector J2 (CON2) Pinout 2 - 24 |

| 2-13 | Rear I/O CompactPCI Bus Connector J2 (CON2) Pinout      |

| 2-14 | External BIOS Setting2 - 30                             |

| 2-15 | Memory Type Selection2 - 30                             |

| 2-16 | Flash Type Selection                                    |

| 2-17 | Fan Power Supply Selection2 - 31                        |

| 2-18 | PCI VI/O setting                                        |

| 2-19 | Shorting Chassis GND (Shield) to Logic GND 2 - 31       |

| 2-20 | Ethernet Interface Configuration                        |

| 2-21 | VGA Interface Configuration2 - 33                       |

| 2-22 | Memory Map for the 1st Megabyte 2 - 33                  |

| 2-23 | I/O Address Map                                         |

| 2-24 | Watchdog Configuration2 - 36                            |

| 2-25 | Reset Control Register 2 - 36                           |

| 2-26 | Onboard Interrupt Configuration                         |

| 2-27 | I/O Status                                              |

| 2-28 | Board ID                                                |

| 2-29 | Hardware Index                                          |

| 2-30 | Jumper Status                                           |

| 2-31 | Logic Version                                           |

| 2-32 | PCI Interrupt Routing2 - 40                             |

| 2-33 | Memory Management2 - 41                                 |

| 2-34 | Flash Socket Page2 - 41                                 |

| 2-35 | Video Resolutions and Display Parameters 2 - 42         |

| 4-1  | Keyboard Commands                                       |

| 4-2  | Description of Drive Specifications                     |

| 4-3  | Diskette Drives                                         |

| 4-4  | Primary Video Subsystem Selection 4 - 11                |

| 4-5  | POST Specific Commands                                  |

| 4-6  | Setting Flash Page Size 4 - 16                          |

| 4-7  | Power Management Modes 4 - 23                           |

| 4-8  | Video-Off Commands                                      |

| 4-9  | Security Options                                        |

| 4-10 | Early POST Codes before System BIOS is Shadowed         |

| 4-11 | Normal POST Codes after System BIOS is Shadowed         |

| A-1  | Technical Specifications                                |

| A-2  | Serial Port Connectors CON2 and CON6 Pinouts (RS232 Mode)  | A - 6  |

|------|------------------------------------------------------------|--------|

| A-3  | Serial Port Connectors CON2 and CON6 Pinouts (RS422 Mode)  | A - 7  |

| A-4  | 26-Pin MDR Connector CON4 Pinout                           | A - 8  |

|      | Pinout of the AT 44-pin EIDE Connector CON5                |        |

| A-6  | Pinout of the AT Standard EIDE Connector CON9              | A - 11 |

| A-7  | Floppy Drive Connector CON3 Pinout                         | A - 13 |

| A-8  | Jumper Setting to Configure COM1                           | A - 14 |

| A-9  | Jumper Setting to Configure COM2                           | A - 14 |

| B-1  | CP302 PMC Module Specifications                            | B - 3  |

| B-2  | Jn1, 32-bit PCI Connector Pinout                           | B - 7  |

| B-3  | Jn2, 32-bit PCI Connector Pinout                           | B - 8  |

| B-4  | CompactPCI Bus Connector J1 (CON1) Pinout                  | B - 9  |

| B-5  | CompactPCI Bus Connector J2 (CON2) Pinout                  | B - 10 |

| C-1  | IDE2 Module Technical Specifications                       | C - 3  |

| C-2  | Serial Port Connectors CON2 and CON6 Pinouts               | C - 7  |

| C-3  | 26-pin MDR Connector Pinout                                | C - 8  |

| C-4  | Pinout of the AT 44-pin Connector                          | C - 9  |

|      | Pinouts of EIDE Connectors CON7 and CON9                   |        |

| C-6  | Floppy Drive Connector CON3 Pinout                         | C - 13 |

| C-7  | Jumper Setting to Configure COM1                           | C - 14 |

| C-8  | Jumper Settings for RS422 RXD Termination (COM1)           | C - 14 |

| C-9  | Jumper Settings for RS422 TXD and RS485 Termination (COM1) | C - 14 |

|      | Jumper Setting to Configure COM2                           |        |

| C-11 | Jumper Settings for RS422 RXD Termination (COM2)           | C - 15 |

| C-12 | Jumper Settings for RS422 TXD and RS485 Termination (COM2) | C - 15 |

| D-1  | Keyboard Connector CON3 Pinout                             | D - 6  |

| D-2  | USB Connector CON4 Pinout                                  | D - 7  |

| D-3  | VGA Connector CON5 Pinout                                  | D - 8  |

| D-4  | RJ45 Connector CON2 Pinout                                 | D - 9  |

| D-5  | Serial Port Connectors CON8 and CON10 Pinouts              | D - 10 |

| D-6  | Fan Control Connector CON9 Pinout                          | D - 11 |

| D-7  | Pinout of AT Standard Connector IDE2                       | D - 11 |

| D-8  | Rear I/O CompactPCI Bus Connector J2 (CON1) Pinout         | D - 13 |

|      | COM1 Configuration using Jumper J2                         |        |

| D-10 | COM2 Configuration using Jumper J1                         | D - 14 |

| D-11 | Shorting Chassis GND (Shield) to Logic GND                 | D - 15 |

### **Revision History**

| Revision History  |                                                                                                              |                                             |    |         |

|-------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------|----|---------|

| Manua             | Manual/Product Title: CP302                                                                                  |                                             |    |         |

| Manual ID Number: |                                                                                                              | 21112                                       |    |         |

| Rev.<br>Index     | Brief Description of                                                                                         | iption of Changes Board Index Date of Issue |    |         |

| 0100              | Initial Issue                                                                                                |                                             | 00 | Apr. 00 |

| 0200              | Inclusion of Minor Improvements                                                                              |                                             | 00 | Jul. 00 |

| 03                | General manual revision and update including<br>addition of chapters for IDE2 module and<br>Rear I/O modules |                                             | 00 | Nov. 00 |

| 04                | Restructuring of Ta                                                                                          | ble of Contents                             | 00 | Nov. 00 |

| 05                | Correction of techn                                                                                          | ical problem in IDE2 chapter                | 00 | Feb. 01 |

|                   |                                                                                                              |                                             |    |         |

|                   |                                                                                                              |                                             |    |         |

This document contains information proprietary to *PEP Modular Computers*. It may not be copied or transmitted by any means, disclosed to others or stored in any retrieval system or media, without the prior written consent of *PEP Modular Computers GmbH* or one of its authorized agents.

The information contained in this document is, to the best of our knowledge, entirely correct. However, *PEP Modular Computers* cannot accept liability for any inaccuracies, or the consequences thereof, nor for any liability arising from the use or application of any circuit, product, or example shown in this document.

PEP Modular Computers reserve the right to change, modify, or improve this document or the product described herein, as seen fit by *PEP Modular Computers* without further notice.

### Trademarks

*PEP Modular Computers* and the *PEP* logo are trademarks owned by *PEP Modular Computers GmbH*, Kaufbeuren, Germany. In addition, this document may include names, company logos and trademarks which are registered trademarks and are, therefore, proprietary of their respective owners.

### **Explanation of Symbols**

#### **CE** Conformity

This symbol indicates that the product described in this manual is in compliance with all applied CE standards. Please see also the section "Applied Standards" in this manual.

#### Caution!

This symbol and title warn you of hazards due to electrical shocks (> 60 V) when touching products or parts of them. Failure to observe the necessary precautions as described and/or prescribed by the law may result in damage to your product and/or endanger your life/health.

Please see also the section "High Voltage Safety Instructions".

#### **ESD-Sensitive Device!**

This symbol and title highlight the fact that electronic boards and their components are sensitive to static electricity. Therefore, care must be taken during all handling operations and inspections of this product, in order to ensure product integrity at all times.

Please read also the section "Special Handling and Unpacking Instructions" on the following pageof this manual.

#### Attention!

This symbol and title emphasize aspects which, if not understood and taken into consideration by the reader, may result in hazards to health and/or material damage.

### Note:

This symbol and title relate to information the user should read through carefully for his or her own advantage.

#### **PEP** Advantage

This symbol and title accompany information highlighting positive aspects of a *PEP* product and/or procedure.

#### Troubleshooting

This symbol and title accompany information about troubleshooting and problem solving.

### For your safety

Your new *PEP* product has been developed and carefully tested in order to provide all the features necessary to ensure full compliance with all electrical safety requirements. It has also been designed for a long fault-free life. However, the life expectancy of your product will be drastically reduced by improper treatment during unpacking and installation. Therefore, in the interests of your own safety and of the correct operation of your new *PEP* product, you are requested to conform with the following guidelines.

### **High Voltage Safety Instructions**

#### Warning!

All operations on this device must be carried out by sufficiently skilled personnel.

#### Caution!

The power supply must always be disconnected before installation, repair and maintenance operations are carried out on this product. Failure to comply with this basic precaution will subject the operator to serious electrical shock hazards. Always unplug the power cable before such operations.

Before installing your new *PEP* product into a system always ensure that your mains power is switched off. This applies also to the installation of piggybacks.

### **Special Handling and Unpacking Instructions**

#### ESD Sensitive Device!

Electronic boards and their components are sensitive to static electricity. Care must therefore be exercised at all times during handling and inspection of the board, in order to ensure product integrity.

- Gerror Do not handle this product while it is outside its protective enclosure while it is not used for operational purposes, unless it is otherwise protected.

- Whenever possible, unpack or pack this product only at EOS/ESD safe work stations. Where safe work stations are not guaranteed, it is important for the user to be electrically discharged before touching the product with his/her hands or tools. This is most easily done by touching a metal part of your system housing.

- It is particularly important to observe standard anti-static precautions when changing piggybacks, ROM devices, jumper settings etc. If the product contains batteries for RTC or memory backup, ensure that the board is not placed on conductive surfaces, including anti-static plastics or sponges. They can cause short circuits and damage the batteries or tracks on the board.

### General Instructions on Usage

- In order to maintain *PEP's* product warranty, this product must not be altered or modified in any way. Changes or modifications to the device, which are not explicitly approved by *PEP Modular Computers* and described in this manual or received from *PEP* Technical Support as a special handling instruction, will void your warranty.

- This device should only be installed in or connected to systems that fulfill all necessary technical and specific environmental requirements. This applies also to the operational temperature range of the specific board version, which must not be exceeded. If batteries are present, their temperature restrictions must be taken into account.

- In performing all necessary installation and application operations, please, follow only the instructions supplied by the present manual.

- Keep all the original packaging material for future storage or warranty shipments. If it is necessary to store or ship the board please re-pack it as nearly as possible in the manner in which it was delivered.

- Special care is necessary when handling or unpacking the product. Please consult the special handling and unpacking instructions on the previous page of this manual.

### **Two Year Warranty**

*PEP Modular Computers* grants the original purchaser of a *PEP* product a *TWO* **YEAR LIMITED HARDWARE WARRANTY** as described in the following. However, no other warranties that may be granted or implied by anyone on behalf of *PEP* are valid unless the customer has the express written consent of *PEP Modular Computers*.

*PEP Modular Computers* warrants their own products, excluding software, to be free from manufacturing and material defects for a period of 24 consecutive months from the date of purchase. This warranty is not transferable nor extendible to cover any other users or long-term storage of the product. It does not cover products which have been modified, altered or repaired by any other party than *PEP Modular Computers* or their authorized agents. Furthermore, any product which has been, or is suspected of being damaged as a result of negligence, improper use, incorrect handling, servicing or maintenance, or which has been damaged as a result of excessive current/voltage or temperature, or which has had its serial number(s), any other markings or parts thereof altered, defaced or removed will also be excluded from this warranty.

If the customer's eligibility for warranty has not been voided he should, in the event of any claim, return the product at the earliest possible convenience to the original place of purchase, together with a copy of the original document of purchase, a full description of the application in which the product has been used and a description of the defect. Please pack the product in such a way as to ensure safe transportation (see our safety instructions).

*PEP* provides for repair or replacement of any part, assembly or sub-assembly at the company's own discretion, or to refund the original cost of purchase, if appropriate. In the event of repair, refunding or replacement of any part, the ownership of the removed or replaced parts reverts to *PEP Modular Computers*, and the remaining portion of the original guarantee, or any new guarantee to cover the repaired or replaced items, will be transferred to cover the new or repaired items. Any extensions to the original guarantee are considered gestures of goodwill, and will be defined in the "Repair Report" issued by *PEP* with the repaired or replaced item.

*PEP Modular Computers* will not accept liability for any further claims resulting directly or indirectly from any warranty claim, other than the above specified repair, replacement or refund. In particular, all claims for damage to any system or process in which the product was employed, or any loss incurred as a result of the product not functioning at any given time, are excluded. The extent of *PEP Modular Computers* liability to the customer shall not exceed the original purchase price of the item for which the claim exists.

*PEP Modular Computers* issues no warranty or representation, either explicit or implicit, with respect to its products' reliability, fitness, quality, marketability or ability to fulfil any particular application or purpose. As a result, the products are sold "as is," and the responsibility to ensure their suitability for any given task remains that of the purchaser. In no event will *PEP* be liable for direct, indirect or consequential damages resulting from the use of our hardware or software products, or documentation, even if *PEP* were advised of the possibility of such claims prior to the purchase of the product or during any period since the date of its purchase.

Please remember that no *PEP Modular Computers* employee, dealer or agent is authorized to make any modification or addition to the above specified terms, either verbally or in any other form, written or electronically transmitted, without the company's prior consent.

### Introduction

| 1.1 | Intr | troduction to CompactPCI               | 1 - 3  |

|-----|------|----------------------------------------|--------|

| 1.2 | PE   | EP Single-height CPU Boards            | 1 - 4  |

| 1.3 | CP   | P302 Product Overview                  | 1 - 4  |

| 1.4 | CP   | P302 Board Introduction                | 1 - 5  |

| 1.5 | CP   | P302 Main Specifications               | 1 - 6  |

| 1.6 | Ροι  | ower Consumption and Temperature Range | 1 - 8  |

| 1.  | .6.1 | Temperature Range                      | 1 - 10 |

|     | 1.6  | 6.1.1 Temperature Range and Air Flow   | 1 - 10 |

| 1.7 | Sof  | oftware Support                        | 1 - 11 |

| 1.8 | Ар   | oplied Standards                       | 1 - 12 |

| 1.  | .8.1 | CE Compliance                          | 1 - 12 |

| 1.  | 8.2  | Mechanical Compliance                  | 1 - 12 |

| 1.  | 8.3  | B Environmental Tests                  | 1 - 12 |

| 1.9 | Rel  | elated Publications                    | 1 - 12 |

| 1.  | .9.1 | CompactPCI Systems/Boards              |        |

This page was intentionally left blank.

### 1. Introduction

### **1.1 Introduction to CompactPCI**

The *PEP Modular Computers* CompactPCI product described in this chapter operates with the PCI bus architecture to support additional I/O and memory-mapped devices as required by various industrial applications. For detailed information concerning the CompactPCI standard, please consult the complete Peripheral Component Interconnect (PCI) and CompactPCI Specifications. For further information regarding these standards and their use, visit the homepage of the *PCI Industrial Computer Manufacturers Group (PICMG)*.

Many system-relevant CompactPCI features that are specific to *PEP Modular Computers* CompactPCI systems may be found described in the *PEP* CompactPCI System Manual. Due to its size, this manual cannot be downloaded via the internet. Please refer to the section "Related Publications" at the end of this chapter for the relevant ordering information.

The CompactPCI System Manual includes the following information:

- Common information that is applicable to all system components, such as safety information, warranty conditions, standard connector pinouts etc.

- All necessary information to combine *PEP Modular Computers* racks, boards, backplanes, power supply units and peripheral devices in a customized CompactPCI system, as well as configuration examples.

- Data on rack dimensions and configurations as well as information on mechanical and electrical rack characteristics.

- Information on the distinctive features of *PEP Modular Computers* CompactPCI boards, such as functionality, hotswap capability. In addition, an overview is given for all existing *PEP Modular Computers* CompactPCI boards with links to the relating datasheets.

- Generic information on the *PEP Modular Computers* CompactPCI backplanes, such as the slot assignment, PCB form factor, distinctive features, clocks, power supply connectors and signalling environment, as well as an overview of the *PEP Modular Computers* CompactPCI standard backplane family.

- Generic information on the *PEP Modular Computers* CompactPCI power supply units, such as the input/output characteristics, redundant operation and distinctive features, as well as an overview of the *PEP Modular Computers* CompactPCI standard power supply unit family.

### 1.2 PEP Single-height CPU Boards

#### Socket 7 Family

The CP312 is a highly integrated 32bit/33 MHz CompactPCI single-board computer that is designed around the Pentium<sup>®</sup> family from Intel<sup>®</sup> and AMD<sup>®</sup>'s K6<sup>™</sup> microprocessors. The VGA interface is integrated within the Chipset. To achieve high CPU and memory performance the board includes 512 kB L2 Cache. DRAM is 32 MB or 64 MB (soldered) which together with the SODIMM provides up to 128 MB main memory.

#### Mobile Pentium<sup>®</sup>III Family

The CP302 is a high performance 64-bit/33MHz CompactPCI system controller boar designed to utilize the Intel<sup>®</sup> Mobile Pentium<sup>®</sup>III Coppermine<sup>™</sup> microprocessors and future processors. This board is based on the Intel<sup>®</sup> 440BX AGP sets and can support CPU speeds of 400 MHz through 700 MHz and host bus speeds up to 100 MHz.

The CP301 is a system controller which is identical to the CP302 in every respect except that it has an additional 4HP front panel interface. The CP301 supports two COM ports and one Fast Ethernet connector on the 4HP interface. The USB and keyboard connector are not available on the 4HP version.

The CP302PM is a non-system controller which is identical to the CP302 apart from having a different PCI/PCI (non-transparent) bridge at J1/J2. This makes possible the addition of further CP302PM's together with a system controller CPU on one CompactPCI bus, i.e. multiprocessing.

#### **1.3 CP302 Product Overview**

The CP302 is a highly integrated single-board computer that is designed around the Intel<sup>®</sup> Mobile Pentium<sup>®</sup> III family of microprocessors. The CP302 is available with either one or two CompactPCI interfaces (depending on version). The version with the 2nd CompactPCI bus is able to address a maximum of 14 slots.

Finding an optimum equilibrium between performance and power dissipation, the CP302 is a reliable Mobile Pentium<sup>®</sup>III controlled board supporting a clock speed of 700 MHz and higher when available.

The CP302 is equipped with a 69030 VGA chip with 4 MB SDRAM memory. Speed of operation is assured by means of the onboard 66 MHz AGP interface. High resolution is provided with the video controller supporting pixel resolutions of up to 1600 x 1200 or up to 16.7 M colors. The board also features a 10BASE-T/100BASE-TX Fast Ethernet based on the Intel<sup>®</sup> 82559 Fast Ethernet PCI Bus Controller.

Designed for stability and packaged in a rugged format, the board fits into all applications situated in industrial environments. The low power consumption of the board is further assured through the use of 3.3 V and 1.5V I/O technology.

The board is compatible with the Microsoft Windows NT<sup>®</sup> operating system. However, the performance of CompactPCI can be tailored to suit real-time applications and operating systems such as Linux<sup>®</sup>, QNX<sup>®</sup> or VxWorks<sup>®</sup> which are instrumental to the success of CompactPCI in these market sectors.

### 1.4 CP302 Board Introduction

The CP302 is a CompactPCI Mobile Pentium<sup>®</sup>III Coppermine<sup>™</sup> based single-board computer specifically designed for use in highly integrated platforms with solid mechanical interfacing for a wide range of industrial environment applications.

Some of the CP302's outstanding features are:

- compliance with CompactPCI Interface 2.0 R3.0

- the option of either one or two independent CompactPCI interfaces

- local PCI bus extender

- suitable for all Intel<sup>®</sup> Mobile Pentium<sup>®</sup>III Coppermine<sup>™</sup> processors in the 495-pin BGA2 package

- up to 256 MB SDRAM main memory, 128 MB soldered with ECC and 128 MB via SODIMM

- 256 kB FLASH for BIOS

- Flash Disk up to 96 MB

- onboard high performance AGP VGA controller

- one EIDE interface, two with Rear I/O version

- one Fast Ethernet device: 10BaseT & 100BaseTX

- integrated Hardware monitor

- optional Rear I/O

The CP302 includes the following commonly used peripheral devices:

- floppy disk interface

- keyboard/USB controller

- two serial ports(ESD protected and EMI compliant)

- counter/timers

- watchdog timer

- real-time clock

- parallel port

### 1.5 CP302 Main Specifications

#### Table 1-1: CP302 Main Specifications

| CP302                       | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                         | Intel <sup>®</sup> Mobile Pentium <sup>®</sup> III Coppermine <sup>™</sup> processor up to 700 MHz<br>with 256 kB L2 on-die cache in 495 BGA2 packaging                                                                                                                                                                                                                                                                                                                                                                    |

| Memory                      | <ul> <li>100 MHz system memory bus</li> <li>256 kB L2 on-die full speed processor cache</li> <li>64 MB up to 128 MB SDRAM via one SODIMM socket running at</li> <li>100 MHz</li> <li>64 up to 128 MB SDRAM soldered with ECC running at 100 MHz</li> <li>512 kB Flash (or optional SRAM with 256 kB or 512 kB)</li> <li>Optional DiskOnChip<sup>™</sup> module up to 96 MB</li> <li>2 x 256 byte EEPROM for storing CMOS data when operating</li> <li>without battery and 2 x 256 byte EEPROM for user purposes</li> </ul> |

| Super I/O                   | <ul> <li>The FDC37C672 from SMSC is an ISA Plug and Play compatible I/O device that provides the following functions:</li> <li>Two 16C550 compatible UARTs with 16 bytes FIFO</li> <li>PS/2 keyboard and mouse interface</li> <li>Floppy disk controller up to 2.88 MB</li> <li>Parallel port ECP/EPP compatible</li> </ul>                                                                                                                                                                                                |

| Chipset                     | Intel <sup>®</sup> 82440BX PCI/AGP controller<br>- GTL processer interface<br>- Integrated DRAM controller<br>- AGP and PCI interface<br>Intel <sup>®</sup> 82371EB PCI/ISA EIDE Xcelerator (PIIX4E)<br>- Multifunction PCI to ISA bridge<br>- Enhanced DMA controller<br>- Interrupt controller based on two 82C59's<br>- Timer based on 82C84<br>- Real-time clock<br>- Power management logic<br>- Supports two USB interfaces<br>- Supports two EIDE interfaces                                                        |

| AGP/VGA<br>interface        | Controller: 69030<br>Video memory: 4 MB<br>Resolution: up to 1600x1200x16 bits per pixel @ 60 Hz                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Fast Ethernet<br>Interface  | Controller: Intel <sup>®</sup> 82559 Fast Ethernet Controller<br>Data Rate: 10 & 100 MBit/s<br>Ethernet: Full 802.2 & 802.3 IEEE compliance supporting 10Base-T<br>and 100Base-TX<br>Cabling: Category 5 two-pair cabling                                                                                                                                                                                                                                                                                                  |

| Software<br>Support         | Award BIOS with Preboot Agent contained within 256 kB of Flash<br>memory. The BIOS parameters are saved in the EEPROM.<br>The CP302 is able to operate without disks, keyboard and video<br>operating systems:<br>Linux <sup>®</sup> , QNX <sup>®</sup> , VxWorks <sup>®</sup> , Windows NT <sup>®</sup> etc.<br>MS-DOS <sup>®</sup> , Windows 95 <sup>®</sup> , 98 <sup>®</sup> , Windows 2000 <sup>®</sup>                                                                                                               |

| CompactPCI Bus<br>Interface | Compatible with CompactPCI Specification V 2.0, Rev. 3.0<br>64-bit/33 MHz master interface 3.3V/5.0V compatible<br><b>Table continued on following page</b>                                                                                                                                                                                                                                                                                                                                                                |

Table continued on following page

#### Table 1-1: CP302 Main Specifications

| CP302                                           | Specifications                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Rear I/O                                        | When the Rear I/O is enabled the CompactPCI interface is configured<br>for 32-bit/33 MHz<br>The 32-bit CompactPCI bus has Rear I/O capability. The following<br>interfaces are routed to the Rear I/O connector J2: COM1 and COM2,<br>PS/2 mouse and keyboard, 2xUSB's, CRT VGA, Ethernet and<br>secondary EIDE port.                                                                                       |  |  |

| PMC Interface                                   | PCI mezzanine connector for standard PMC module. 32-bit/33 MHz master interface 3.3V/5.0V compatible                                                                                                                                                                                                                                                                                                        |  |  |

| General                                         | Dimensions: 100 mm x 160 mm<br>Operating temp.: 0°C to +60°C<br>E1 (optional): -25°C to +75°C<br>E2 (optional): -40°C to +85°C<br>Storage temp.: -55°C to +85°C<br>Operating humidity: 0% to 95% non-condensing<br>Weight: CP302 4HP without heatsink: 200g<br>CP302 4HP with heatsink: 278g<br>CP302 8HP with heatsink: 322g<br>CP302 I/O module: 66g<br>CP302 PMC module: 110g                            |  |  |

| Front Panel<br>Interfaces                       | PS-2 style connector for Keyboard/Mouse via Y-cable<br>(6-pin mini-DIN)<br>COM1: 9-pin D-sub (RS232, RS422,RS485)<br>COM2: 9-pin D-sub (RS232, RS422, RS485)<br>USB: one 4-pin connector<br>Parallel port: 25-pin high density D-sub<br>Ethernet: one RJ-45 connector<br>VGA: 15-pin D-sub SVGA connector<br>LED's: ACT, SPEED: Ethernet status<br>LED: TH: Overtemperature status<br>Reset button, guarded |  |  |

| Onboard<br>interfaces                           | One EIDE interface (two EIDE interfaces with Rear I/O version)<br>supporting Ultra/DMA for 2/4 devices (HardDisks or CD-ROM's) on<br>40-pin 2.54mm connectors<br>One floppy disk interface (up to 2.88 MB)<br>PCI extension connection                                                                                                                                                                      |  |  |

| Thermal<br>Management /<br>System<br>Monitoring | Watchdog: software configurable watchdog generates IRQ, SMI or<br>hardware reset         Hardware monitor: LM81 monitoring temperature, fan speed and all<br>onboard voltages         Temperature monitor: MAX 1617 monitoring the CPU on-die and<br>board temperature                                                                                                                                      |  |  |

| Hotswap-<br>Compatible                          | The CP302 supports the addition or removal of other boards whilst in<br>a powered-up state. Individual clocks for each slot and Enum signal<br>handling are in compliance with the PCIMG 2.1 Hotswap<br>Specification.                                                                                                                                                                                      |  |  |

| Common<br>Features                              | DC power monitors (3.3V and 5V)<br>Battery socket and 3.0V lithium battery for RTC:<br>VARTA Type CR2025<br>PANASONIC BR2020                                                                                                                                                                                                                                                                                |  |  |

### **1.6 Power Consumption and Temperature Range**

The CP302 board is based on the Intel<sup>®</sup> Mobile Pentium<sup>®</sup>III processor. Intel<sup>®</sup> has developed mobile processors to meet the specific needs of mobile PC's. As such, they operate at lower voltages than their desktop counterparts, are significantly smaller in size, consume less power and dissipate less heat. The design is optimized for low power consumption applications.

The goal of this description is to provide a method to calculate the power consumption for the CP302 base board and for additional configurations. The processor dissipates the majority of the thermal power.

The power consumption table lists the voltage and current specifications for the CP302 board and the CP302 accessories. The values are measured with a 8 slot passive CompactPCI backplane and two power supplies, one for the CPU and the other one for the harddisk. During the measurement the power consumption of the backplane can be ignored. The operating systems was DOS 6.22 without power management and Windows NT 4.0 with power management. The measured values varied, because the power depended on the processor activity. All Mobile Pentium<sup>®</sup>III processors are powered with 1.35V core voltage (low power version).

These values were measured at the DOS prompt and without the keyboard.

| Power                                                         | 5V    | 3.3V  | Total  |

|---------------------------------------------------------------|-------|-------|--------|

| 400 MHz<br>32 or 64 MB Memory (128 Mbit chips)<br>without VGA | 5.2W  | 5.3W  | 10.5W  |

| 400 MHz<br>64 or 128 MB Memory<br>with VGA                    | 5,3W  | 6.5W  | 11.8W  |

| 500 MHz<br>64 or 128 MB Memory<br>with VGA                    | 5.9W  | 6.5W  | 12.4W  |

| 700 MHz<br>64 or 128 MB Memory<br>with VGA                    | 8.8 W | 6.4 W | 15.2 W |

#### Table 1-2: Power Consumption Table with DOS Running (without keyboard)

| Power                                                         | 5V    | 3.3V  | Total |

|---------------------------------------------------------------|-------|-------|-------|

| 400 MHz<br>32 or 64 MB Memory (128 Mbit chips)<br>without VGA | 1.2W  | 4.7W  | 5.9W  |

| 400 MHz<br>64 or 128 MB Memory<br>with VGA                    | 1.2W  | 5.9W  | 7.1W  |

| 500 MHz<br>64 or 128 MB Memory<br>without VGA                 | 1.4W  | 5.9W  | 7.3W  |

| 700 MHz<br>64 or 128 MB Memory<br>without VGA                 | 2.0 W | 5.8 W | 7.8 W |

### Table 1-3: Power Consumption Table with Windows NT 4.0 Running (no application started and without keyboard)

The 400 MHz version without VGA is not a standard version. For more information please contact *PEP*.

| Table 1-4: Power Consumption Table f | or CP302 Accessories |

|--------------------------------------|----------------------|

|--------------------------------------|----------------------|

| Module                                 | Power 5V | Power 3.3V |

|----------------------------------------|----------|------------|

| Keyboard                               | 100 mW   |            |

| 64 MB SODIMM module                    |          | 500 mW     |

| 128 MB SODIMM module                   |          | 500 mW     |

| DiskOnChip™ 16 MB                      | 100 mW   |            |

| DiskOnChip™ 144 MB                     | 100 mW   |            |

| CP302 IO module without HardDisk drive | 100 mW   |            |

| CP302 PMC module                       |          |            |

| CP302 PMC + second CPCI interface      |          | 300 mW     |

#### 1.6.1 Temperature Range

The CP302 family are the first CompactPCI boards capable of operating over the extended temperature range from -40°C up to + 85°C. All onboard components are specially selected for the higher temperature range. For the higher temperatures the desktop processors are not suitable, because the power consumption is higher and the allowable case temperature is lower. The only suitable processor is the Intel<sup>®</sup> Mobile Pentium<sup>®</sup>III processor family. These processors are produced with the new 0.18-micron process which have lower power consumption and support higher case temperatures (100°C).

#### 1.6.1.1 Temperature Range and Air Flow

These values have been measured with typical applications under DOS and Windows NT 4.0. In worst case situations the values and the temperature range must be reduced accordingly. For all situations the maximum case temperature of the Mobile Pentium III processor must be below 100°C. This temperature value can be measured with the onboard remote temperature sensor. In instances of overtemperature the hardware monitor will reduce the processor clock to lower the generated power.

| Heat Sink<br>Version | Range        | 400 MHz | 500 MHz | 700 MHz |

|----------------------|--------------|---------|---------|---------|

| 4HP                  | 0°C - 60°C   | 0 m/s   | 0 m/s   | 0.2 m/s |

|                      | -25°C - 75°C | 0 m/s   | 0.6 m/s |         |

|                      | -40°C - 85°C | 0.6 m/s |         |         |

|                      | 0°C - 60°C   | 0 m/s   | 0 m/s   | 0 m/s   |

| 8HP                  | -25°C - 75°C | 0 m/s   | 0 m/s   | 1.0 m/s |

|                      | -40°C - 85°C | 0 m/s   |         |         |

Table 1-5: Typical Temperature Range and Required Air Flow

0 m/s air flow means standard convection cooling with the board in an upright position. An airflow of 1 m/s is a typical value for a standard *PEP* ASM 4 rack ( 3U CompactPCI rack with 1U cooling fans ). For other racks or housings the available airflow will be different. The maximum ambient temperature must be recalculated and / or measured for such environments. For the calculation of the maximum ambient temperature the processor case temperature must never exceed 100°C. The maximum heatsink temperature depends on the physical characteristics of the heatsink and thermal connection to the processor. To ensure that the heatsink temperature does not exceed its limits an airflow may be needed for a given ambient temperature. Heatsink temperature is measured at the top of the heatsink base, closest to the processor.

Important Warning concerning overheating follows on next page

#### Important:

It is the responsibility of the end user to ensure that the processor case temperate never exceeds 100° Celsius in order to protect the board against overheating. Permanent overheating can damage the board.

If the temperature on the processor die is greater than 100°C the maximum ambient temperature must be reduced or an external airflow must be provided by means of an additional fan.

### **1.7 Software Support**

Real-time operating systems such as QNX<sup>®</sup>, VxWorks<sup>®</sup>, and others are supported. The standard PC features supported by the BIOS also allow for PC operating systems such as Linux<sup>®</sup>, MS-DOS<sup>®</sup>, Windows 9X<sup>®</sup>, Windows 2000<sup>®</sup>, Windows NT 4.0<sup>®</sup> (Embedded).

### 1.8 Applied Standards

#### **1.8.1 CE Compliance**

The *PEP Modular Computers'* CompactPCI systems comply with the requirements of the following CE-relevant standards:

- Emission EN50081-1

- Immission EN50082-2

- Electrical Safety EN60950

#### 1.8.2 Mechanical Compliance

• Mechanical Dimensions IEEE 1101.10

#### 1.8.3 Environmental Tests

| ٠ | Vibration/Broad-Band | IEC68-2-6              |

|---|----------------------|------------------------|

|   | Random Vibration     | IEC68-2-64 (3U boards) |

- Permanent Shock IEC68-2-29

- Single Shock IEC68-2-27

#### **1.9 Related Publications**

#### 1.9.1 CompactPCI Systems/Boards

• CompactPCI Specification, V. 2.0, Rev. 3.0

| 2.1 Fu  | nctional Block Diagram                 | 2 - 4  |

|---------|----------------------------------------|--------|

| 2.2 Fro | ont Panels                             | 2 - 5  |

| 2.3 Во  | ard Layouts                            | 2 - 6  |

| 2.4 Ma  | ain Features                           | 2 - 8  |

| 2.4.1   | CPU                                    | 2 - 8  |

| 2.4.2   | Memory                                 | 2 - 8  |

| 2.4.3   | Interrupts                             | 2 - 8  |

| 2.5 Pe  | ripherals                              | 2 - 9  |

| 2.5.1   | Watchdog Timer                         | 2 - 9  |

| 2.5.2   | Battery                                | 2 - 9  |

| 2.5.3   | Reset                                  | 2 - 10 |

| 2.5.4   | SMBus Devices                          | 2 - 11 |

| 2.5.5   | Thermal Management / System Monitoring | 2 - 11 |

| 2.5.6   | Serial EEPROM                          | 2 - 12 |

| 2.5.7   | Flash Memory                           | 2 - 13 |

| 2.5.8   | PCI- to-PCI Bridge                     | 2 - 13 |

| 2.6 Bo  | ard Interfaces                         | 2 - 14 |

| 2.6.1   | Keyboard/Mouse Interface               | 2 - 14 |

| 2.6     | 6.1.1 Keyboard Connector CON4 Pinout   | 2 - 14 |

| 2.6.2   | USB Interface                          | 2 - 15 |

| 2.6     | 6.2.1 USB Connector CON5 Pinout        | 2 - 15 |

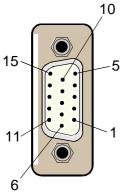

| 2.6.3   | VGA Interface                          | 2 - 16 |

| 2.6     | 5.3.1 VGA connector CON8 Pinout        | 2 - 16 |

| 2.6.4 Fast Ethernet Interface                               | 2 - 17 |

|-------------------------------------------------------------|--------|

| 2.6.4.1 RJ45 Connector CON10 Pinout                         | 2 - 17 |

| 2.6.5 Ethernet LED Status                                   | 2 - 17 |

| 2.6.6 Fan Power Supply                                      | 2 - 18 |

| 2.6.7 EIDE Interfaces                                       | 2 - 18 |

| 2.6.7.1 EIDE Connector CON7 Pinout                          | 2 - 19 |

| 2.6.8 Floppy Drive Interface                                | 2 - 21 |

| 2.6.8.1 Floppy Disk Connector CON13 Pinout                  | 2 - 21 |

| 2.6.8.2 PCI Extension Connector CON6                        | 2 - 22 |

| 2.6.8.3 I/O Interface Connectors CON3 and CON11             | 2 - 22 |

| 2.6.9 CompactPCI Bus Interface(s)                           | 2 - 22 |

| 2.6.9.1 CompactPCI Connectors CON1 and CON2 Pinouts         |        |

| 2.6.10 Rear I/O Interface                                   | 2 - 25 |

| 2.6.10.1 Rear I/O Configuration Illustration                | 2 - 26 |

| 2.6.10.2 Optional Rear I/O interface on CPCI Connector CON2 | 2 - 27 |

| 2.6.10.3 Rear I/O Jumper Setting                            | 2 - 28 |

| 2.7 Jumper Description                                      | 2 - 30 |

| 2.7.1 External BIOS                                         | 2 - 30 |

| 2.7.2 Memory Type Selection                                 | 2 - 30 |

| 2.7.3 Flash Type Selection                                  |        |

| 2.7.4 Fan Power Supply Selection                            |        |

| 2.7.5 PCI VI/O setting                                      |        |

| 2.7.6 Shorting Chassis GND (Shield) to Logic GND            | 2 - 31 |

| 2.7.7     | Jumper Setting for Rear I/O2       | - 32 |

|-----------|------------------------------------|------|

| 2.7.8     | Reserved Jumpers2                  | - 33 |

| 2.8 Mer   | тогу Мар2                          | - 33 |

| 2.9 Spe   | ecial Registers Description2       | - 35 |

| 2.9.1     | Watchdog2                          | - 35 |

| 2.9.      | .1.1 Watchdog Trigger2             | - 35 |

| 2.9.      | .1.2 Watchdog Timer2               | - 36 |

| 2.9.2     | Reset Control Register2            | - 36 |

| 2.9.3     | Interrupt Configuration Register2  | - 37 |

| 2.9.4     | I/O Status2                        | - 38 |

| 2.9.5     | Board ID2                          | - 38 |

| 2.9.6     | Hardware Index2                    | - 39 |

| 2.9.7     | Jumper Status2                     | - 39 |

| 2.9.8     | Logic Version2                     | - 40 |

| 2.9.9     | PCI Interrupt Routing2             | - 40 |

| 2.9.10    | Memory Management of Flash Socket2 | - 41 |

| 2.9.11    | Flash Socket Page2                 | - 41 |

| 2.10 Vide | eo Resolutions2                    | - 42 |

### 2. Functional Description and Configuration

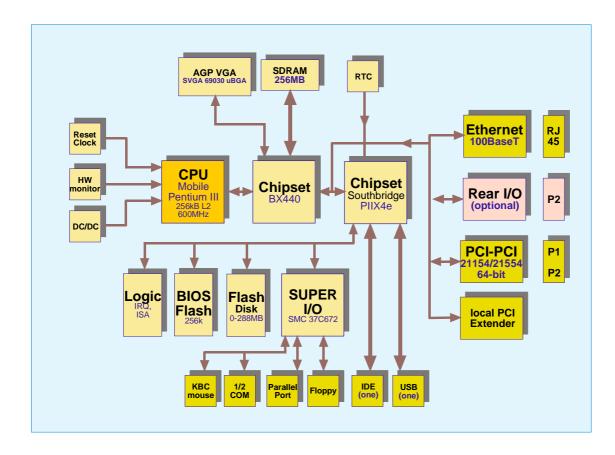

### 2.1 Functional Block Diagram

Figure 2-1: CP302 Functional Block Diagram

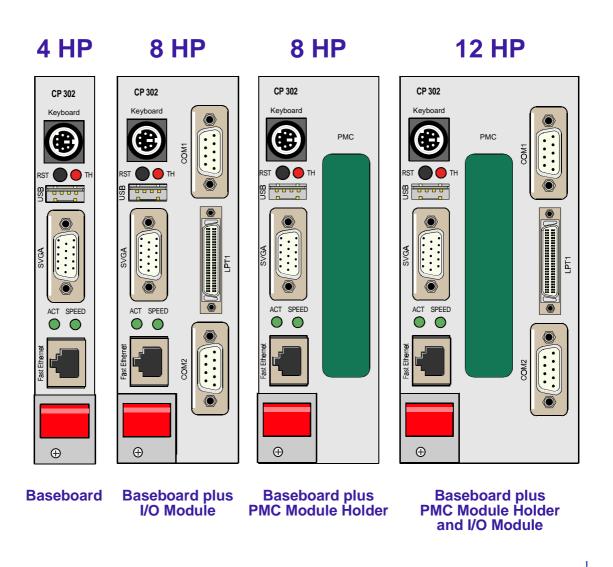

#### 2.2 Front Panels

The front panel includes one LED placed under the keyboard/mouse interface connector ("Board LED's") and two LED's placed over the Ethernet connector ("Ethernet LED"). The functions of the LED's are as follows:

Board LED:

• TH (red) = Temperature alarm; if ON, an overtemperature has occurred. The CPU clock speed is reduced automatically.

Ethernet LED's:

- ACT (green) = if ON link is active and transmission is in progress via the Ethernet link.

- SPEED (green) = if ON transmission speed is 100 MBit/s.

#### Figure 2-2: CP302 Front Panels

### 2.3 Board Layouts

Figure 2-3: CP302 Board Layout (Front Side)

# 2.4 Main Features

The following descriptions highlight the main features of the principal functional blocks of the CP302.

## 2.4.1 CPU

The CP302 supports the Intel<sup>®</sup> Mobile Pentium<sup>®</sup>III Coppermine<sup>™</sup> processor family up to 700MHz with 256 kB L2 on-die cache in a 495-pin BGA2 package. The processor speed is automatically selected. The onboard voltage regulator is automatically programmed by the processor's VID pins to provide the required voltage. All supported onboard memory can be cached.

## 2.4.2 Memory

The CP302 has two locations for installing memory; up to 128 MB may be soldered with ECC and a further 128 MB may be added by means of the onboard SODIMM socket. The board supports a maximum of 256 MB. All installed memory will be automatically detected, so there is no need to set any jumpers. All PC/100 compliant SDRAM on 144-pin gold SODIMM's are supported by the CP302 board.

| Onboard | SODIMM | ECC Support   |

|---------|--------|---------------|

| 64MB    |        | Enabled       |

| 64MB    | 64 MB  | Not supported |

| 64MB    | 128 MB | Not supported |

| 128MB   |        | Enabled       |

| 128MB   | 64 MB  | Not supported |

| 128MB   | 128 MB | Not supported |

Table 2-1: Memory Options Utilizing SODIMM Sockets

All memory components and SODIMM's used with this board must comply with the following PC SDRAM specifications:

- PC SDRAM Specification PC100

- PC Serial Presence Detect Specification

## 2.4.3 Interrupts

Two enhanced 8259-style interrupt controllers provide a total of fifteen interrupt inputs with features which include level and edge-triggered inputs, fixed and rotating priorities and individual input masking. Interrupt sources include: Counter/timers, serial I/O, RTC, keyboard/mouse, printer, floppy disk, EIDE interfaces and four interrupt sources on the CompactPCI backplane.

# 2.5 Peripherals

The following standard peripherals are available on the CP302 board:

Real-Time Clock

The real-time clock performs time-keeping functions and includes 256 bytes of general purpose battery-backed CMOS RAM. Features include an alarm function, programmable periodic interrupt and a 100-year calendar. All battery-backed CMOS RAM data remains stored in an additional EEPROM. This prevents data loss.

Counter/Timer

Three 8254-style counter/timers are included on the CP302 as defined for the PC/AT.

## 2.5.1 Watchdog Timer

A watchdog timer is provided, which forces an IRQ5, NMI or Reset condition (configurable in the watchdog register). The watchdog time can be programmed in 12 steps ranging from 125 msec up to 256 seconds. If the watchdog timer is enabled, it cannot be stopped.

#### 2.5.2 Battery

The CP302 is provided with a 3.0V "coin cell" lithium battery for the RTC.

To replace the battery please proceed as follows:

- Turn off power

- Remove the battery

- Place the new battery in the socket.

- Make sure that you insert the battery the right way round. The plus pole must be on the top!

The lithium battery must be replaced with an identical battery or a battery type recommended by the manufacturer. Suitable batteries include the VARTA CR2025 and PANASONIC BR2020

Important notes concerning the battery appear on the next page

#### Important

- Care must be taken to ensure that the battery is correctly replaced.

- The battery should be replaced only with an identical or equivalent type recommended by the manufacturer.

- Dispose of used batteries according to the manufacturer's instructions.

- The typical life expectancy of a 170 mAh battery (VARTA CR2025) is 4 5 years with an average on-time of 8 hours per working day at an operating temperature of 30°C. However, this typical value varies considerably because the life expectancy is dependent on the operating temperature and the standby time (shutdown time) of the system in which it operates.

To ensure that the lifetime of the battery has not been exceeded it is recommended to exchange the battery after 3 - 4 years.

## 2.5.3 Reset

The CP302 is automatically reset by a precision voltage monitoring circuit that detects a drop in voltage below the acceptable operating limit of 4.725 V for the 5V line and below 3.0V for the 3.3V line, or in the event of a power failure of the DC/DC converter. Other reset sources include the watchdog timer and local push-button switch. The CP302 responds to any of these sources by initializing local peripherals and issuing the PCIRST\* signal on the CompactPCI bus.

The CP302 has a variety of reset options:

- Front panel push button

- Watchdog

- Backplane reset (PRST input)

- Power control (5V, 3.3V and CPU core voltage)

#### 2.5.4 SMBus Devices

The CP302 provides a System Management Bus (SMBus) for access to several system monitoring and configuration functions. The SMBus consists of a two-wire I2C bus interface. The following table describes the function and address of every onboard SMBus device.

#### Table 2-2: SMBus Device Addresses

| Device                     | SMB Address |

|----------------------------|-------------|

| PIIX4 slave port           | 0001000Xb   |

| Temperature sensor MAX1617 | 0011000Xb   |

| Hardware Monitor LM81      | 0101100Xb   |

| EEPROM                     | 1010XXXXb   |

### 2.5.5 Thermal Management / System Monitoring

The LM81 can be used to monitor several critical hardware parameters of the system, including power supply voltages, fan speeds and temperatures; all of which are very important for the proper operation and stability of a high-end computer system. The LM81 provides an I2C<sup>™</sup> serial bus interface.

The voltages of the onboard power supply (+12 V, -12V, +5V, +3.3V, +1.5V, Vcore) are supervised. The onboard hardware monitor is able to detect the CPU fan speed and an external fan speed in revolutions per minute (RPM). The presence of the fans is automatically detected.

The integrated MAX1617 temperature sensors monitor the CPU temperature to make sure that the system is operating at a safe temperature level. If the temperature is too high, the sensors automatically reduces the CPU clock frequency, depending on the mode chosen in the BIOS set.

**CP302**

## 2.5.6 Serial EEPROM

A serial EEPROM is provided, organised into 4 blocks with 256 bytes per block (24LC08). This EEPROM is connected to the I2C<sup>™</sup> bus provided by the PIIX4E.

#### Table 2-3: EEPROM Address Map

| Address   | Function                        |

|-----------|---------------------------------|

| 1010000xb | SODIMM SPD                      |

| 1010001xb | Onboard SPD                     |

| 1010010xb | Not available                   |

| 1010011xb | Not available                   |

| 1010100xb | VxWorks parameter (24LC08)      |

| 1010101xb | Free for user purposes (24LC08) |

| 1010110xb | Free for user purposes (24LC08) |

| 1010111xb | CMOS backup (24LC08)            |

It is strongly recommended that users access only the two free EEPROM banks

## 2.5.7 Flash Memory

There are two Flash devices available as described below, one for the BIOS and one 32-pin socket for a flexible Flash configuration.

#### 1. BIOS Flash

The CP302 uses a 256 kB flash memory to store BIOS firmware. It can be updated as new versions of the BIOS become available. You may easily upgrade your BIOS using the AWARD *awdflash* utility.

#### 2. Socket Memory

Different flash module versions are available. In order to achieve flexibility with low cost the flash memory is not soldered, but connected via a special module from M-Systems (DiskOnChip<sup>™</sup> 2000).

- Standard flash memory of up to 512 KB in a 32-pin DIL package

- AMD29F010

- AMD29F040

- Standard EEPROM memory in a 32-pin DIL package

- AMD27C010

- AMD27C020

- DiskOnChip<sup>™</sup> flash memory:

- 8 96 MB

For higher flash memory capacity it is recommended to use an ATA flash disk.

## 2.5.8 PCI- to-PCI Bridge

The Intel<sup>®</sup> 21154 bridge is a 64-bit 33 MHz PCI-to-PCI bridge device. It supports up to seven CompactPCI loads through a passive backplane.

The 21154 is a second generation PCI-to-PCI bridge and is fully compliant with the PCI Local Bus Specification Rev. 2.1. The 64-bit interface interoperates transparently with either 64-bit or 32-bit devices.

The PC-to-PCI bridge allows the primary and secondary PCI bus to operate concurrently. A master and target on the same PCI bus can communicate while the other PCI bus is busy.

# 2.6 Board Interfaces

## 2.6.1 Keyboard/Mouse Interface

The onboard keyboard controller is 8042 software compatible.

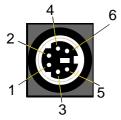

## Figure 2-5: Keyboard/Mouse Connector

The PC/AT standard keyboard/mouse connector is a PS/2-type 6-pin shielded mini-DIN connector. The keyboard power supply unit is protected by a 500 mA fuse. All signal lines are EMI-filtered.

A special adapter to connect a mouse device and/or a keyboard to the PS/2 connector ia available from *PEP*

## 2.6.1.1 Keyboard Connector CON4 Pinout

The CP302 has the AT keyboard connector implemented on a 6-pin Mini-Din connector.

A special adapter to connect a mouse device and/or keyboard to the PS/2 connector is available from *PEP*.

| Pin | Name  | Function       | In/Out |

|-----|-------|----------------|--------|

| 1   | KDATA | Keyboard data  | In/Out |

| 2   | MDATA | Mouse data     | In/Out |

| 3   | GND   | Ground signal  |        |

| 4   | VCC   | VCC signal     |        |

| 5   | KCLK  | Keyboard clock | Out    |

| 6   | MCLK  | Mouse clock    | Out    |

#### Table 2-4: Keyboard Connector CON4 Pinout

## Note:

The keyboard power supply is protected with a fuse (500mA) and all the signal lines are EMI-filtered.

## 2.6.2 USB Interface

The Universal Serial Bus, or USB, is a versatile port. This one port type can function as a serial, parallel, mouse, keyboard, or joystick port and is capable of supporting up to 127 daisy-chained peripheral devices.

#### Figure 2-6: USB Connector